# MOS Memory Data Book

1984

**European Edition**

Commercial and Military Specifications

# IMPORTANT NOTICE

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Texas Instruments assumes no responsibility for infringement of patents or rights of others based on Texas Instruments applications assistance or product specifications, since TI does not possess full access to data concerning the use or applications of customer's products. TI also assumes no responsibility for customer product designs.

Copyright © 1984 by Texas Instruments Incorporated

| Alphanumeric Index, Table of Contents, Selection Guide | 1   |

|--------------------------------------------------------|-----|

|                                                        |     |

| Interchangeability Guide                               | 2   |

|                                                        |     |

| Glossary/Timing Conventions/Data Sheet Structure       | 3   |

|                                                        |     |

| Dynamic RAM and Memory Support Devices                 | 4   |

|                                                        |     |

| Dynamic RAM Modules                                    | 5   |

|                                                        |     |

| EPROM Devices                                          | 6   |

|                                                        | * . |

| ROM Devices                                            | 7   |

|                                                        |     |

| Static RAM and Memory Support Devices                  | 8   |

|                                                        |     |

| Applications Information                               | 9   |

|                                                        |     |

| Logic Symbols                                          | 10  |

|                                                        |     |

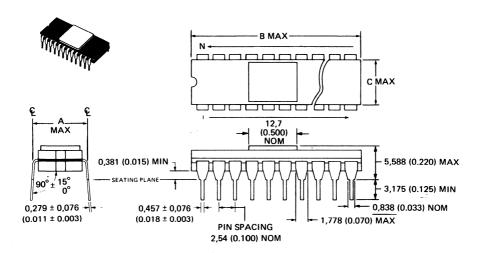

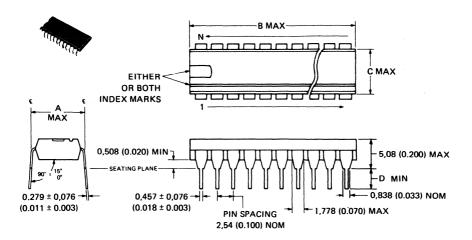

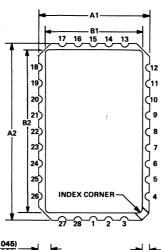

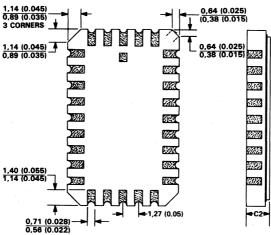

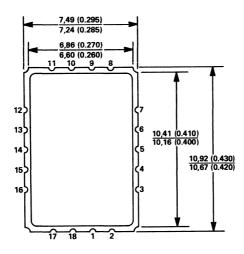

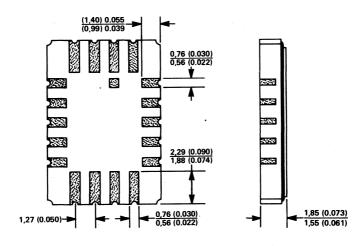

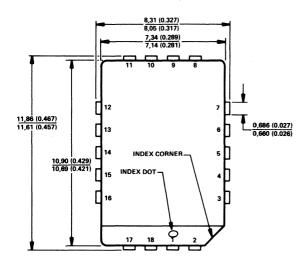

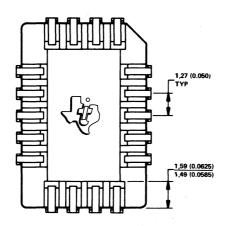

| Mechanical Data                                        | 11  |

# **ALPHANUMERIC INDEX TO DATA SHEETS**

|            | Page |          | Page  |

|------------|------|----------|-------|

| SMJ2516    | 6-1  | TMS2516  | 6-1   |

| SMJ2532    | 6-11 | TMS2532  | 6-11  |

| SMJ2564    | 6-21 | TMS2564  | 6-21  |

| SMJ2708    | 6-31 | TMS2708  | 6-31  |

| SMJ27L08   | 6-31 | TMS27L08 | 6-31  |

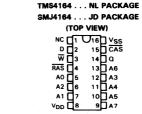

| SMJ4164    | 4-39 | TMS2732A | 6-47  |

| SMJ4416    | 4-85 | TMS2764  | 6-53  |

| SMJ5517    | 8-25 | TMS4016  | 8-13  |

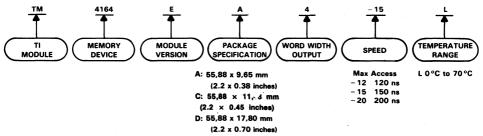

| TM4416ET16 | 5-1  | TMS4044  | 8-19  |

| TM4416EJ16 | 5-1  | TMS40L44 | 8-19  |

| TM4416EE8  | 5-5  | TMS4116  | 4-1   |

| TM4416EF8  | 5-5  | TMS4161  | 4-15  |

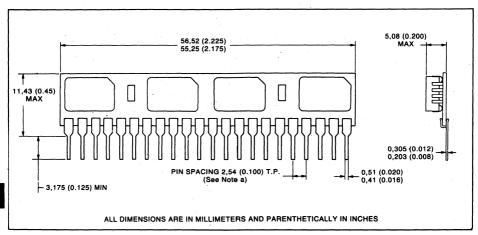

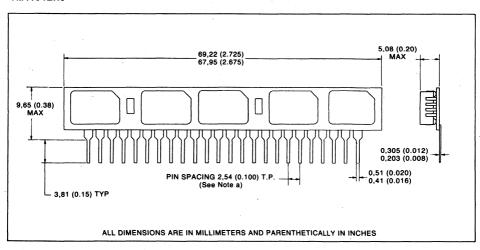

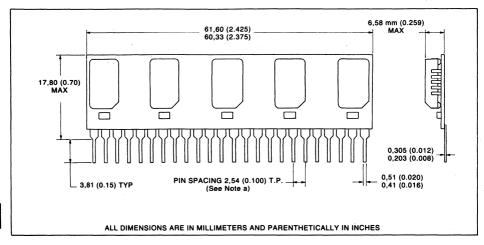

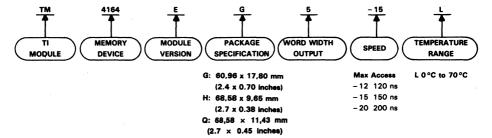

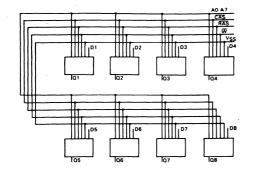

| TM4164EA4  | 5-9  | TMS4164  | 4-39  |

| TM4164EC4  | 5-9  | TMS4256  | 4-63  |

| TM4164ED4  | 5-9  | TMS4257  | 4-63  |

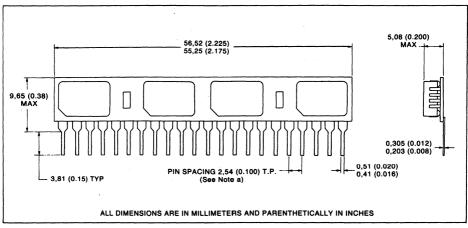

| TM4164EG5  | 5-15 | TMS4416  | 4-85  |

| TM4164EH5  | 5-15 | TMS4464  | 4-107 |

| TM4164EQ5  | 5-15 | TMS4500A | 4-125 |

| TM4164EK8  | 5-19 | TMS4664  | 7-1   |

| TM4164FN9  | 5-23 | TMS4732  | 7-7   |

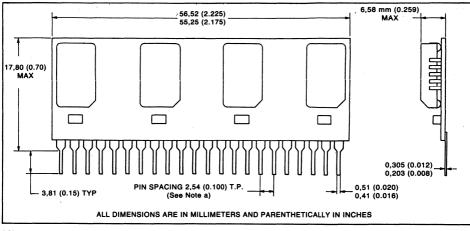

| TM4164FC1  | 5-27 | TMS4764  | 7-13  |

| TM4164FA1  | 5-27 | TMS4964  | 7-19  |

| TMS2114    | 8-1  | TMS27128 | 6-61  |

| TMS2114L   | 8-1  | TMS47128 | 7-27  |

| TMS2150    | 8-7  | TMS47256 | 7-37  |

|            |      |          |       |

|            |      |          |       |

| ALPHANUMERIO       | C INDEX, TABLE      | OF CONTENT    | S. SELECTION ( | GUIDE              |       |

|--------------------|---------------------|---------------|----------------|--------------------|-------|

|                    | ·                   |               |                |                    | 1-1   |

| •                  |                     |               |                |                    | 1-3   |

|                    |                     |               |                |                    | 1-5   |

| 10 1110, 110.      | 110, 21 1101110 00. |               |                |                    |       |

| INTERCHANGE        | ABILITY GUIDE       |               |                |                    |       |

|                    |                     | Part Numberii | ng (Examples)  |                    | 2-1   |

|                    |                     |               |                |                    | 2-8   |

|                    |                     |               |                |                    | 2-8   |

|                    |                     |               |                |                    | 2-9   |

|                    |                     |               |                |                    | 2-10  |

| 2                  |                     |               |                |                    |       |

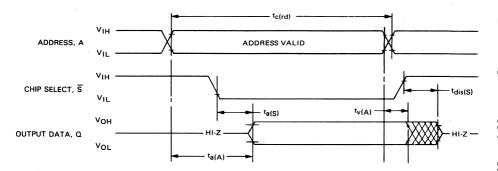

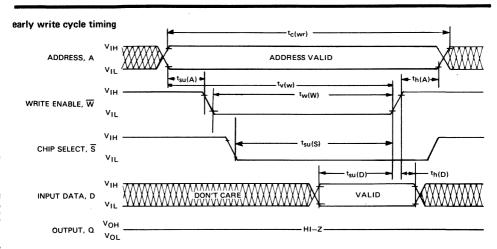

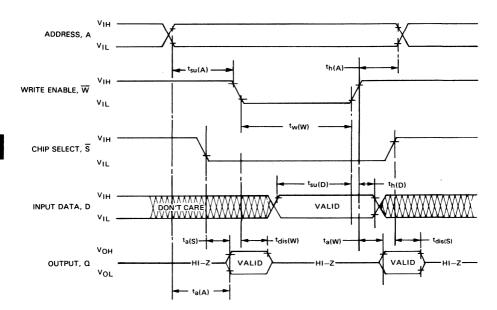

| GLOSSARY/TIM       | ING CONVENTIO       | NS/DATA SHI   | EET STRUCTURE  |                    |       |

| Part I —           | General Concepts    | and Types of  | f Memories     |                    | 3-1   |

|                    | •                   | • • •         |                | ng Letter Symbols) | 3-3   |

|                    |                     |               |                |                    | 3-8   |

|                    |                     |               |                |                    | 3-8   |

|                    | Daoio Data Circo    |               |                |                    | •     |

| DYNAMIC RAM        | and MEMORY SI       | JPPORT DEV    | ICES           |                    |       |

| TMS4116            | 16,384-bit          |               |                |                    | 4-1   |

| TMS4161            | 65,536-bit          |               |                |                    | 4-15  |

| SMJ4164            | 65,536-bit          | •             | •              |                    | 4-39  |

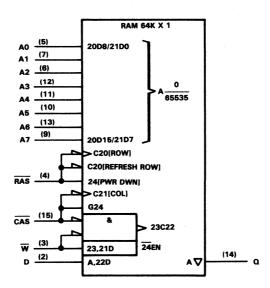

| TMS4164            | 65,536-bit          | , ,           |                |                    | 4-39  |

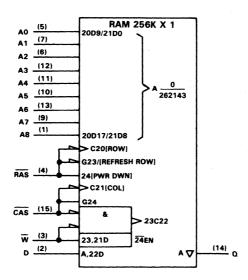

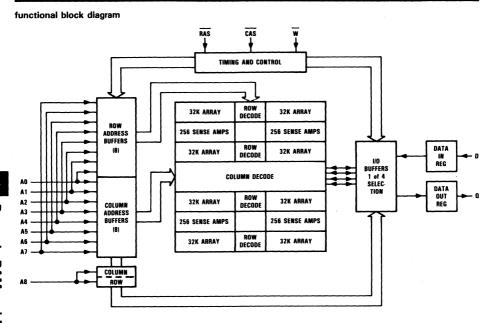

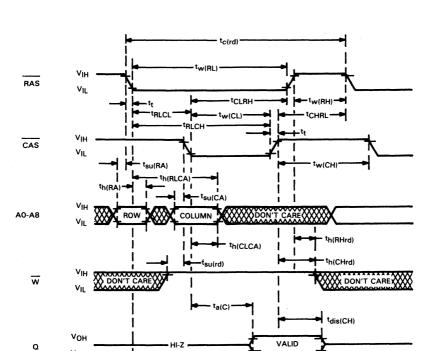

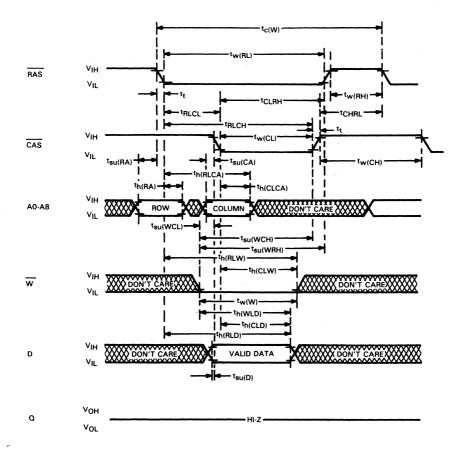

| TMS4256            | 262,144-bit         | , ,           |                |                    | 4-63  |

| TMS4257            | 262,144-bit         |               |                |                    | 4-63  |

| SMJ4416            | 65,536-bit          | •             |                |                    | 4-85  |

| TMS4416            | 65,536-bit          |               |                | ,                  | 4-85  |

| TMS4464            | 262,144-bit         |               |                |                    | 4-107 |

| TMS4500A           |                     |               |                |                    | 4-107 |

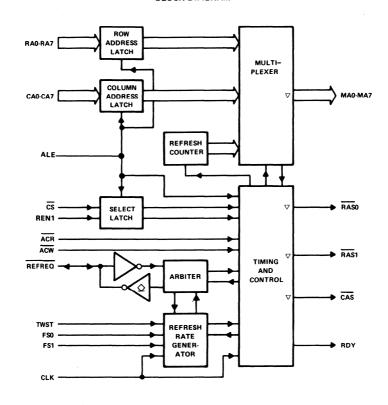

| TWIS4SOUA          | Dynamic haw         | Controller    |                |                    | 4-125 |

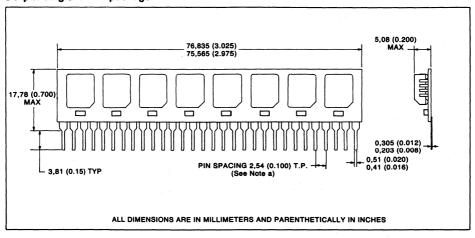

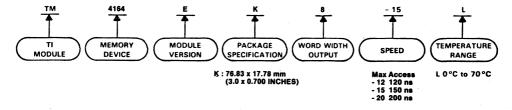

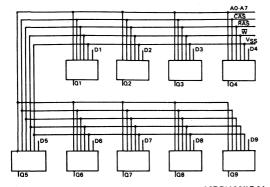

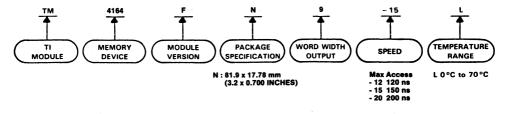

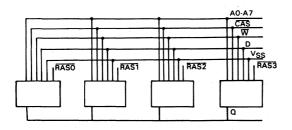

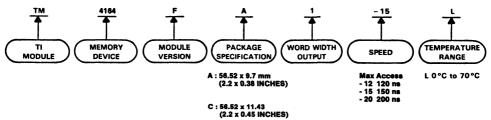

| DYNAMIC RAM        | MODULES             |               |                |                    |       |

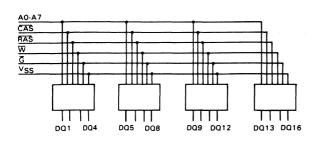

|                    | 16-TM4416EJ16       |               | 262 144-bit    | (16K×16)           | 5-1   |

|                    | 8-TM4416EF8         |               |                | (32K×8)            | 5-6   |

|                    | 4-TM4164EC4-TM      | 14164FD4      |                | (64K×4)            | 5-9   |

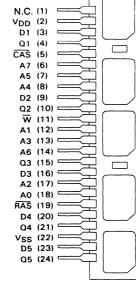

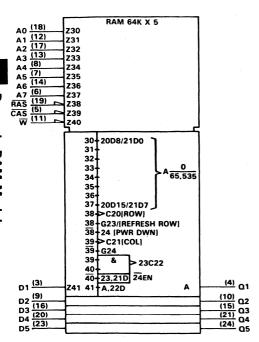

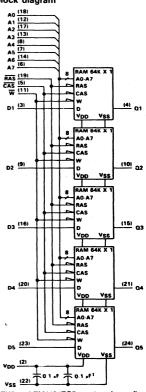

|                    | i5-TM4164EH5-TM     |               | •              | (64K×5)            | 5-15  |

| TM4164EK           |                     | 14 TOLGO      |                | (64K×8)            | 5-19  |

| TM4164EN           |                     |               |                | (64K×9)            | 5-19  |

|                    | 1-TM4164FA1         |               |                | (256K × 1)         | 5-27  |

| 11014104FC         | 1-11VI4 104FA 1     |               | 202,144-01     | (250K x 1)         | 5-27  |

| EPROM DEVICE       | =0                  |               |                |                    |       |

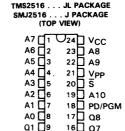

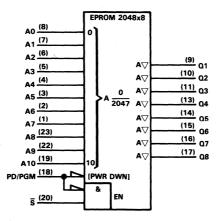

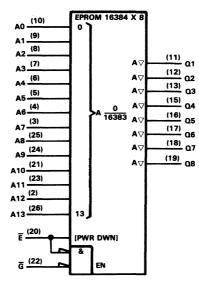

| SMY2516            | 5 V                 | 16,384-bit    | (2K ∨ 8)       |                    | 6-1   |

| TMS2516            | 5 V                 | 16,384-bit    |                |                    | 6-1   |

| SMJ2532            | 5 V                 | 32,768-bit    | • •            |                    | 6-11  |

| 5MJ2532<br>TMS2532 | 5 V<br>5 V          | 32,768-bit    |                | ••••••             | 6-11  |

|                    | 5 V<br>5 V          |               |                |                    |       |

| SMJ2564            |                     | 65,536-bit    |                |                    | 6-21  |

| TMS2564            | 5 V                 | 65,536-bit    |                |                    | 6-21  |

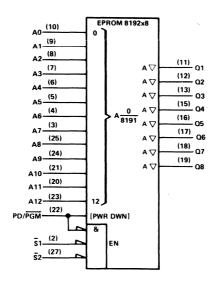

| SMJ2708            | 3-Supply            | 8,192-bit     |                | •••••              | 6-31  |

| TMS2708            | 3-Supply            | 8,192-bit     |                |                    | 6-31  |

| SMJ27L08           | 3-Supply            | 8,192-bit     | (1K×8)         |                    | 6-31  |

# TABLE OF CONTENTS (Concluded)

|     | TMS27L08     | 3-Supply           | 8,192-bit      | (1K×8)                                | 6-31         |

|-----|--------------|--------------------|----------------|---------------------------------------|--------------|

|     | TMS2716      | 3-Supply           | 16,384-bit     | (2K×8)                                | 6-41         |

|     | TMS2732A     | 5 V                | 32,768-bit     | (4K×8)                                | 6-47         |

|     | TMS2764      | 5 V                | 65,536-bit     | (8K×8)                                | 6-53         |

|     | TMS27128     | 5 V                | 131,072-bit    | (16K×8)                               | 6-61         |

|     |              |                    |                |                                       |              |

| RO  | M DEVICES    |                    | 222            |                                       | 7-1          |

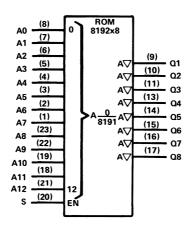

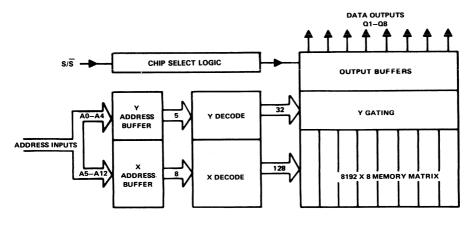

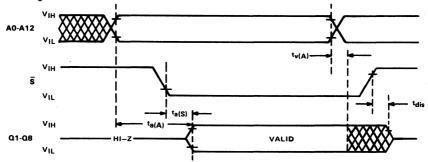

|     | TMS4664      | 5 V                | 65,536-bit     | (8K×8)                                | 7-1<br>7-7   |

|     | TMS4732      | 5 V                | 32,768-bit     | (4K×8)                                | 7-7<br>7-13  |

|     | TMS4764      | 5 V                | 65,536-bit     | (8K×8)                                | 7-13<br>7-19 |

|     | TMS4964      | 5 V                | 65,536-bit     | (8K×8)                                |              |

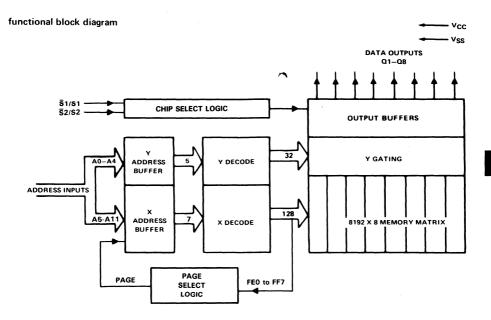

|     | TMS47128     | 5 V                | 131,072-bit    | (16K×8)                               | 7-27         |

|     | TMS47256     | 5 V                | 262,144-bit    | (32K×8)                               | 7-37         |

|     |              |                    | ODT DE\#05     |                                       |              |

| STA |              | MEMORY SUPP        | ORT DEVICE     |                                       | 8-1          |

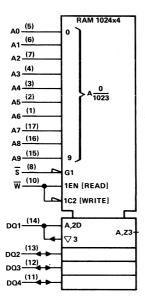

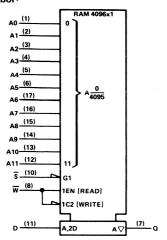

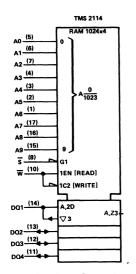

|     | TMS2114      | 4,096-bit          |                |                                       | 8-1          |

|     | TMS2114L     | 4,096-bit          | (1K×4)         |                                       | 8-7          |

|     | TMS2150      |                    | Comparator     |                                       | 8-13         |

|     | TMS4016      | 16,384-bit         |                |                                       |              |

|     | TMS4044      | 4,096-bit          |                |                                       | 8-19         |

|     | TMS40L44     | 4,096-bit          | (4K×1)         |                                       | 8-19         |

|     | SMJ5517      | 16,384-bit         | (2K×8)         |                                       | 8-25         |

|     |              |                    |                |                                       |              |

| API | PLICATIONS I | NFORMATION         |                | Davis Ossaideretions                  | 9-1          |

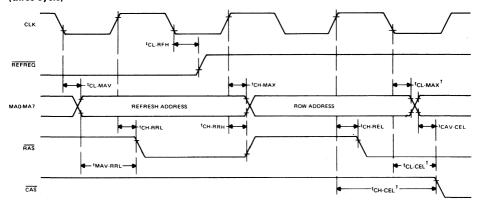

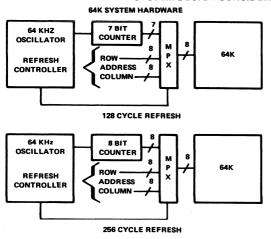

|     | 64K Dynami   | ic RAM Refresh A   | nalysis Syste  | m Design Considerations               | 9-3          |

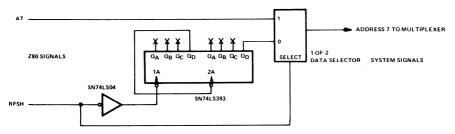

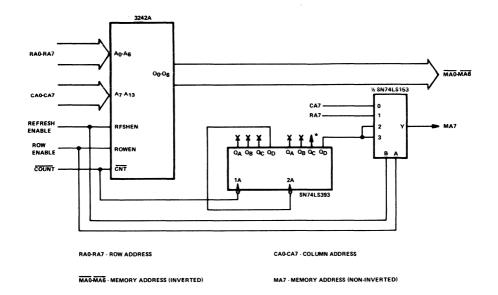

|     | 256-Cycle F  | lefresh Conversion | n <u></u> .    | · · · · · · · · · · · · · · · · · · · | 9-3          |

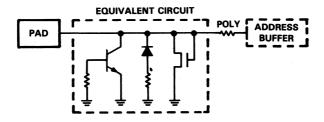

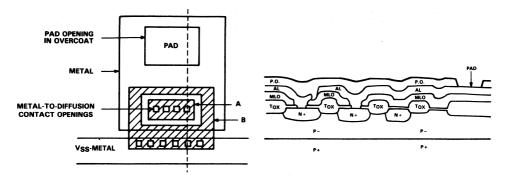

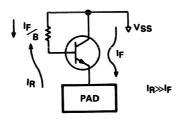

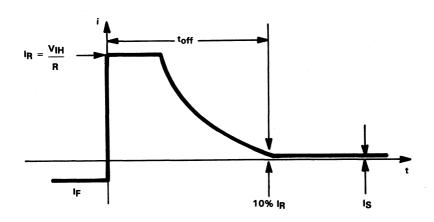

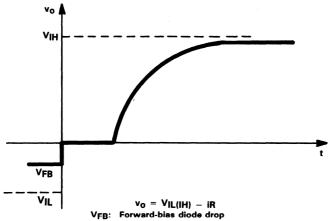

|     | TMS4164A     | and TMS4416 Inp    | out Diode Pro  | otection                              | 9-7<br>9-11  |

|     | TMS4164 a    | nd TMS4416 Inter   | lock Clock .   |                                       |              |

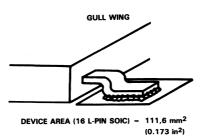

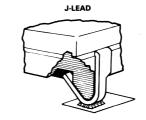

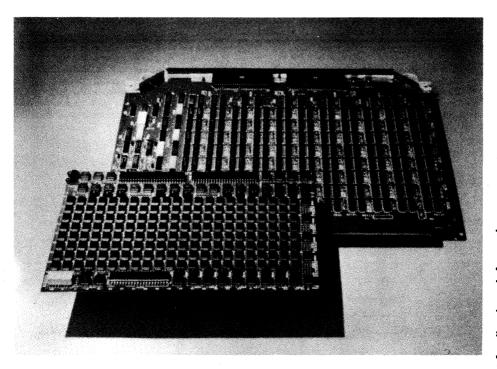

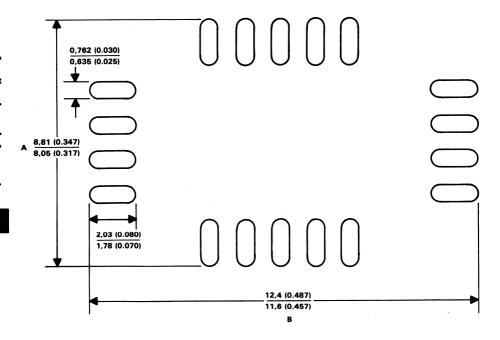

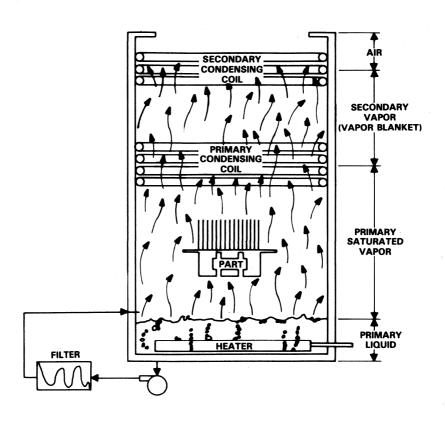

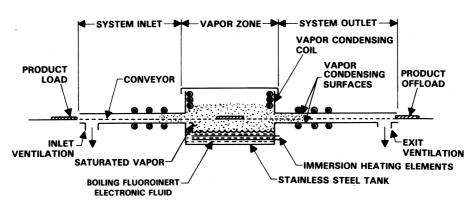

|     | Introduction | to Surface Moun    | t Technology   |                                       | 9-15         |

|     | TTL Drivers  | for TMS4416-15     |                |                                       | 9-25         |

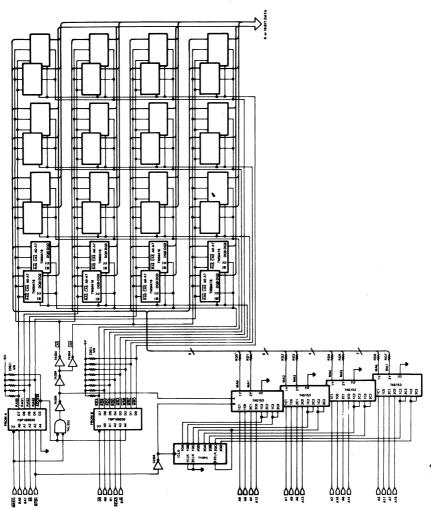

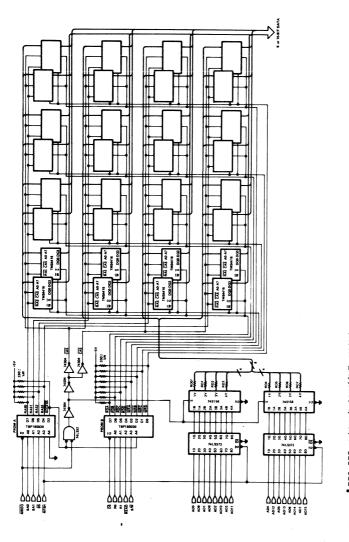

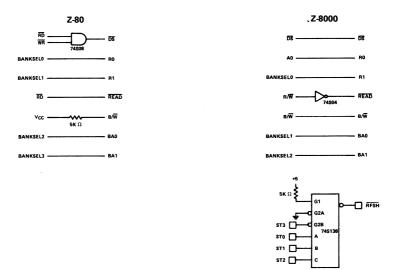

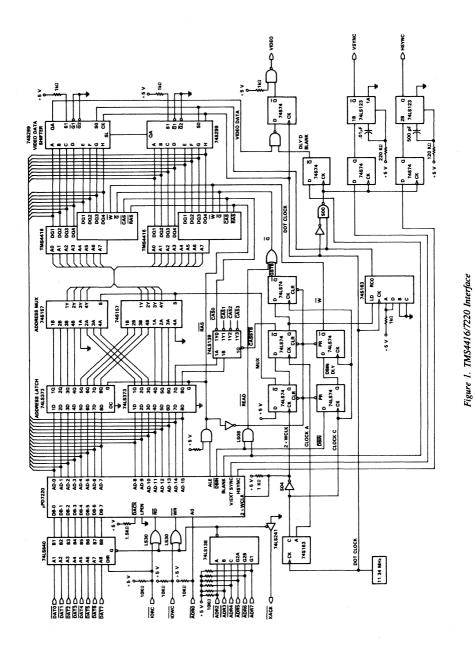

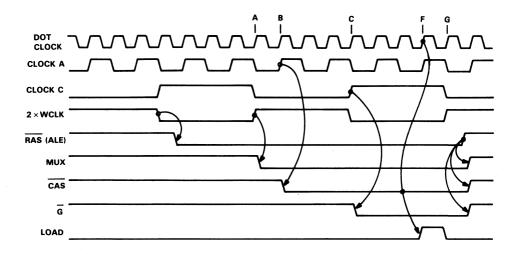

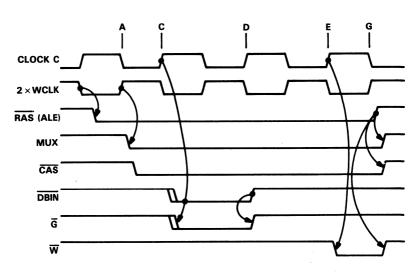

|     | TMS4416/72   | 220 Graphics       |                |                                       | 9-31         |

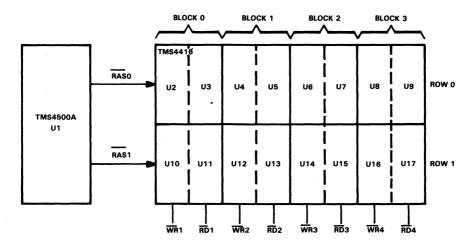

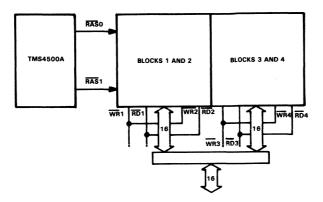

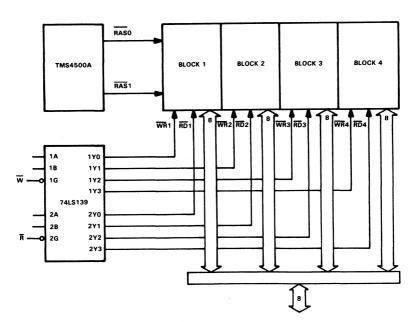

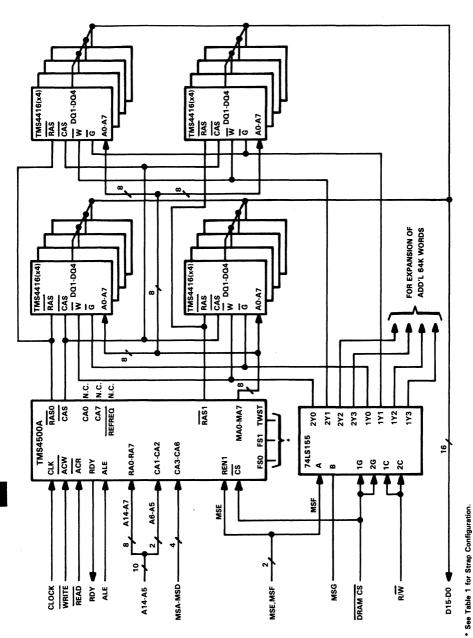

|     | TMS4416/T    | MS4500A Evaluati   | ion Board      |                                       | 9-39         |

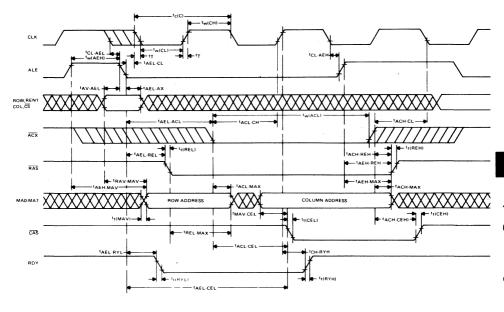

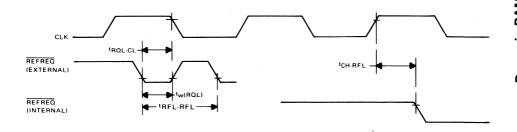

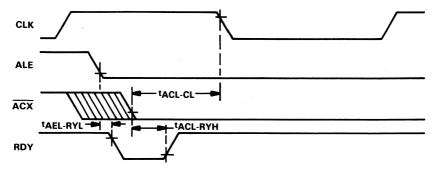

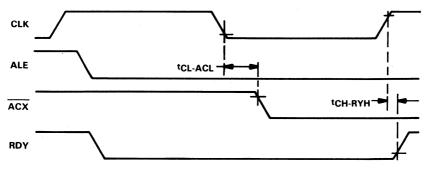

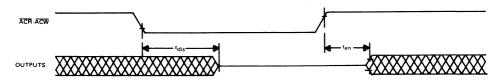

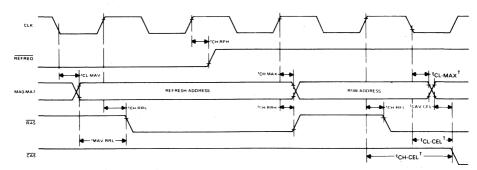

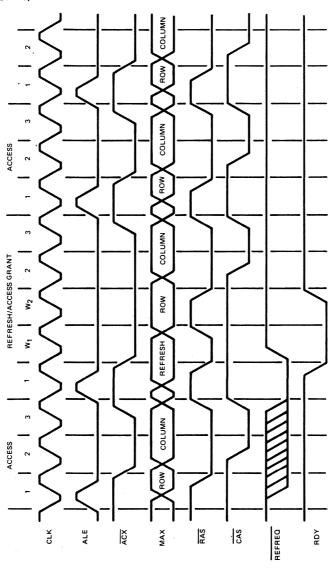

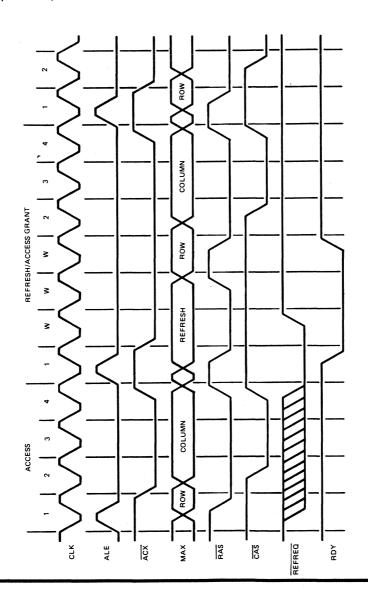

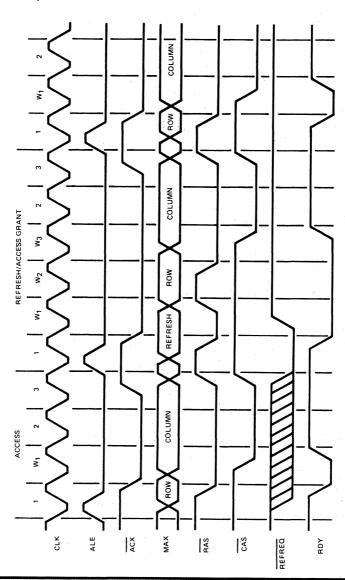

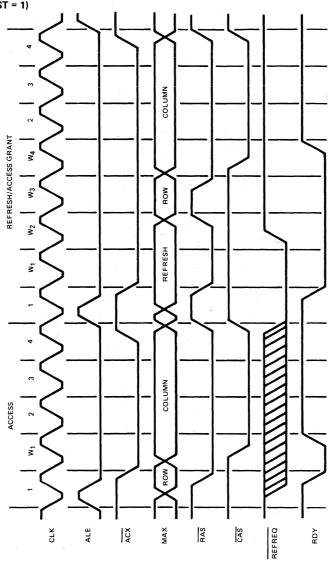

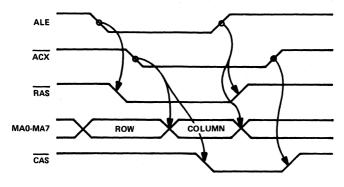

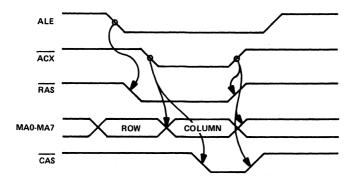

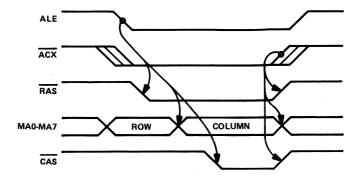

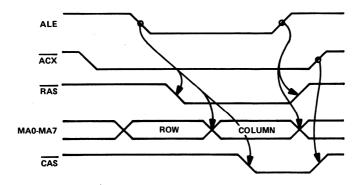

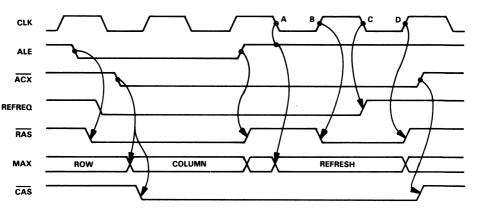

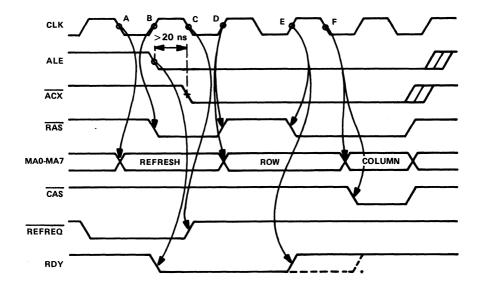

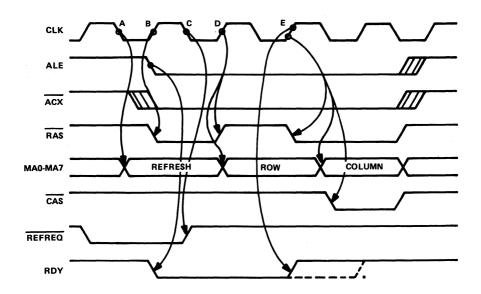

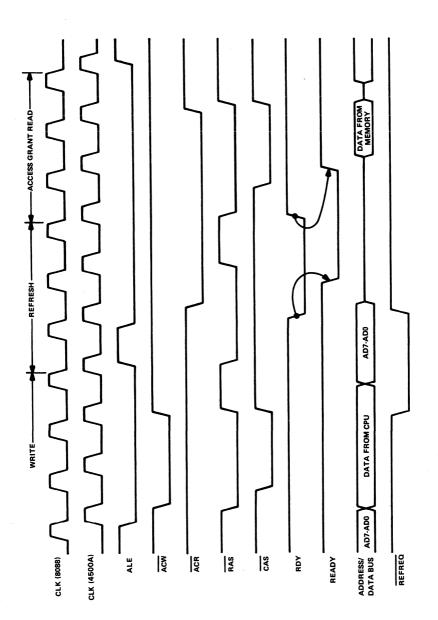

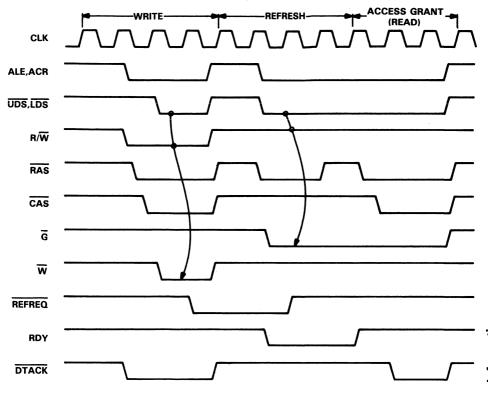

|     | TMS4500A     | ALE and ACX Tim    | ning           | ·                                     | 9-45         |

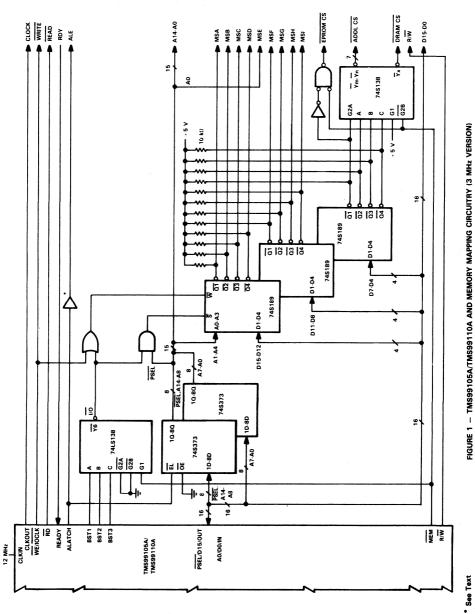

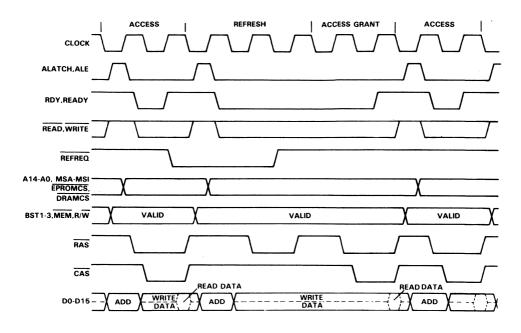

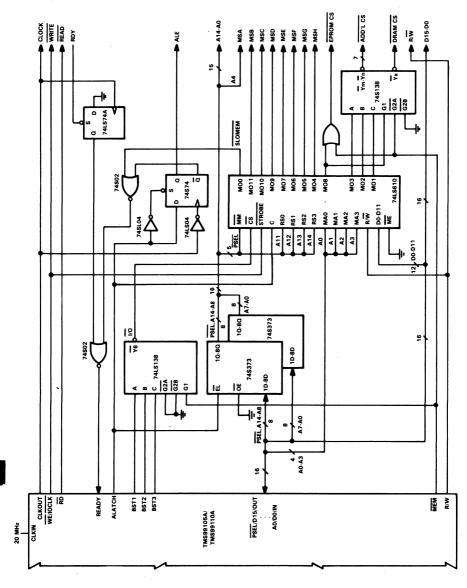

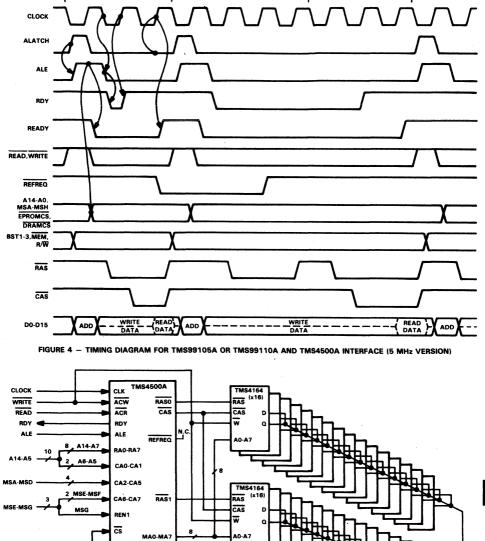

|     | TMS4500A     | DRAM Controller    | Configured for | or the TMS99000 Series                |              |

|     | 16-Bit Mi    | croprocessors      |                |                                       | 9-5          |

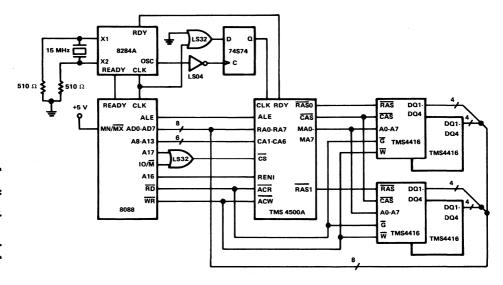

|     | TMS4500A/    | 8088 Interface     |                |                                       | 9-63         |

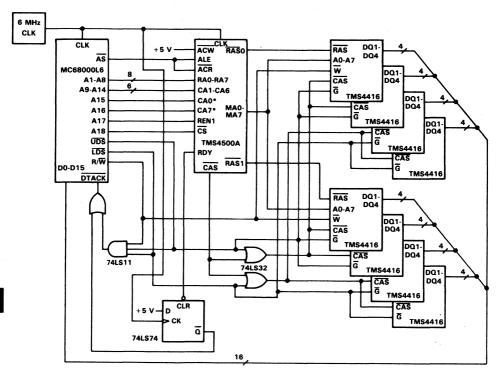

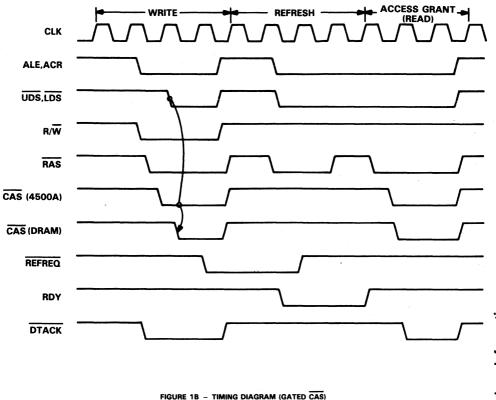

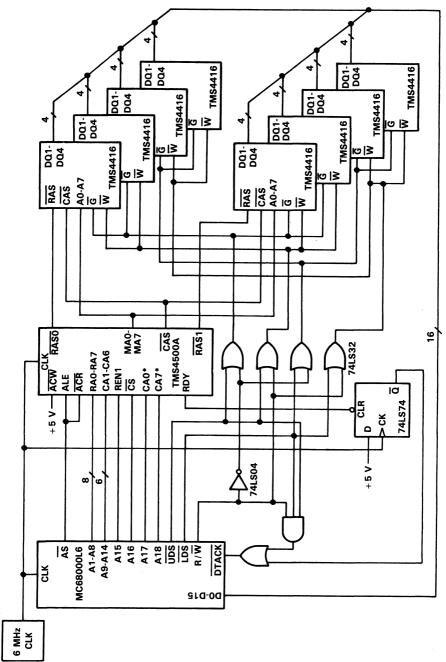

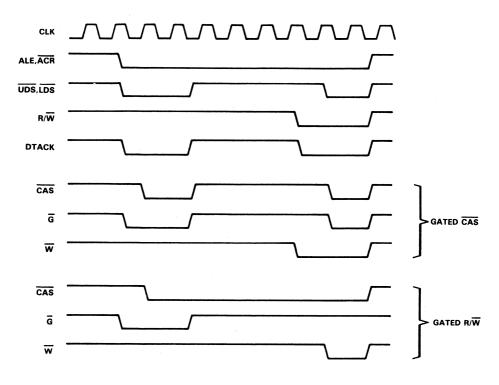

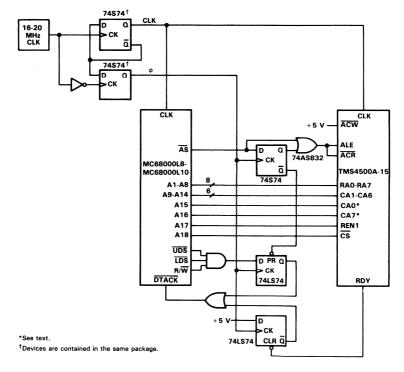

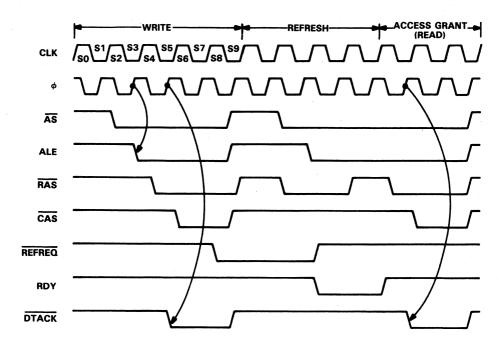

|     | TMS4500A/    | MC68000 Interfac   | А              |                                       | 9-69         |

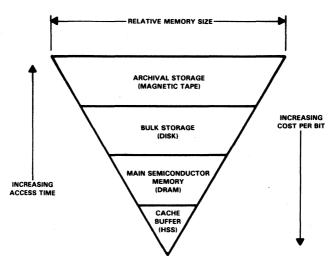

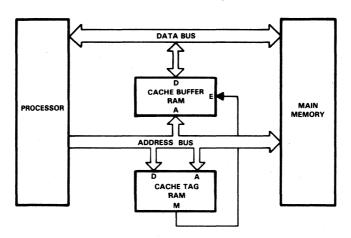

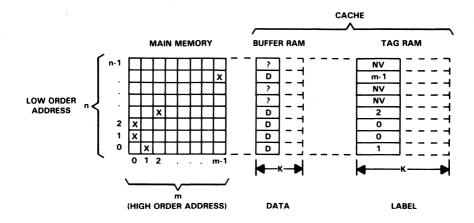

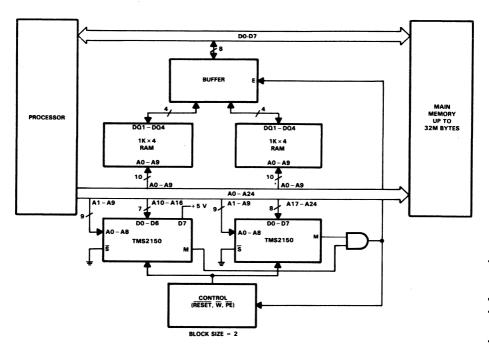

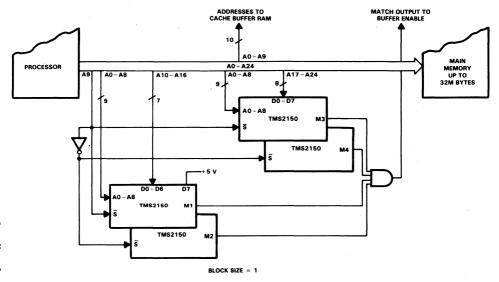

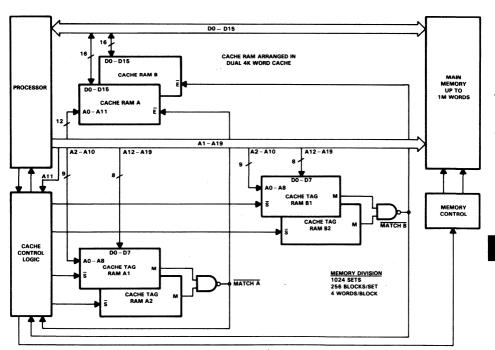

|     | An Introduc  | tion to Cache Mei  | mory System    | s and the TMS2150                     | 9-8          |

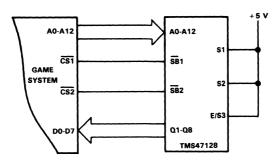

|     | High Densit  | ty ROMs In Consu   | imer Game S    | Systems                               | 9-93         |

|     | ~            | =                  |                |                                       |              |

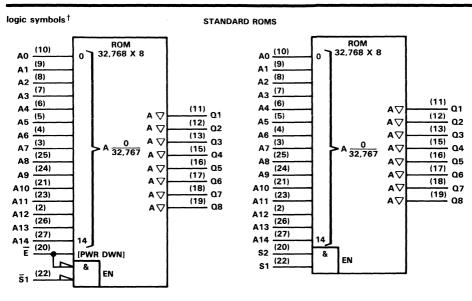

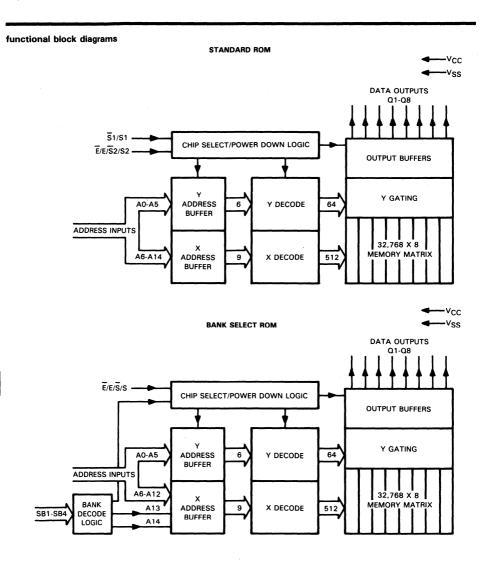

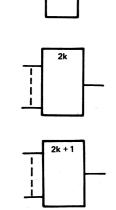

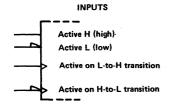

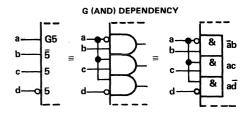

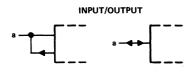

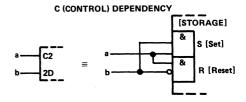

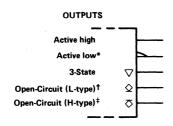

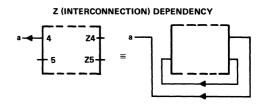

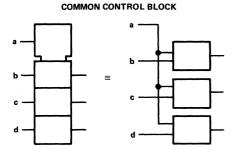

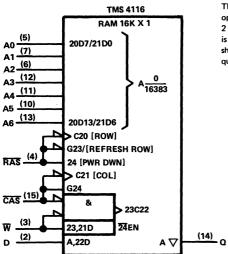

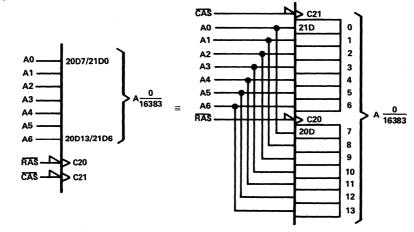

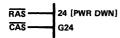

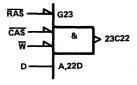

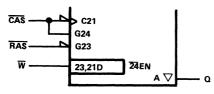

| LO  | GIC SYMBOL   | S                  |                |                                       |              |

|     | Explanation  | of New Logic Sy    | mbols for M    | emories                               | 10-          |

|     | •            |                    |                |                                       |              |

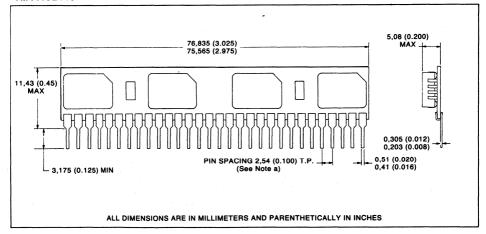

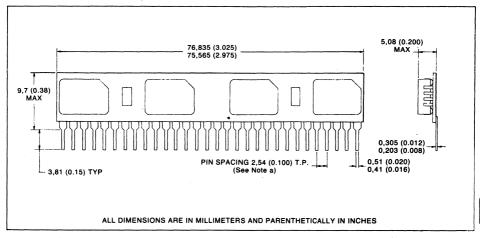

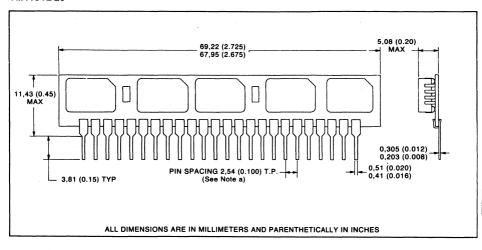

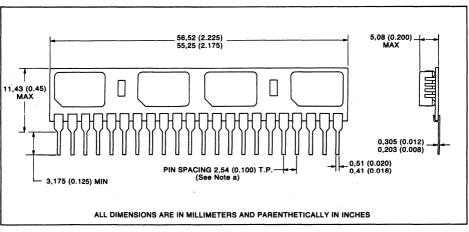

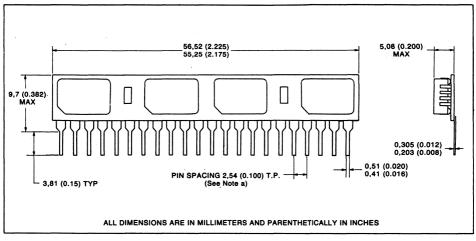

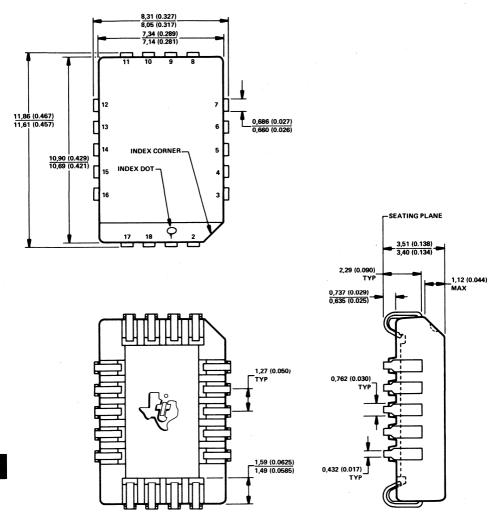

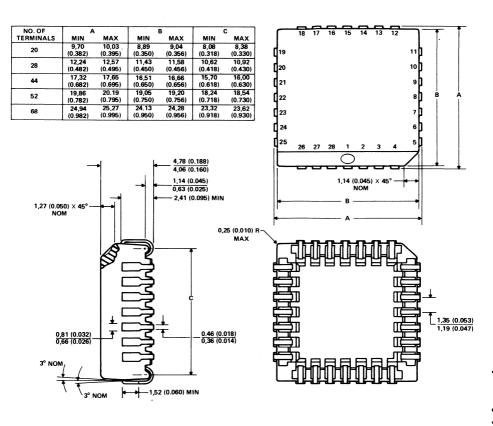

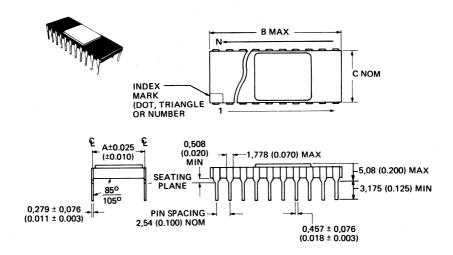

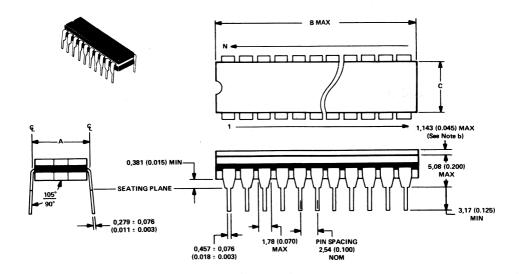

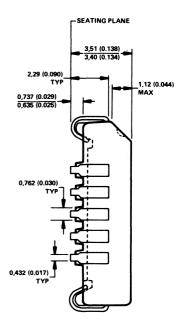

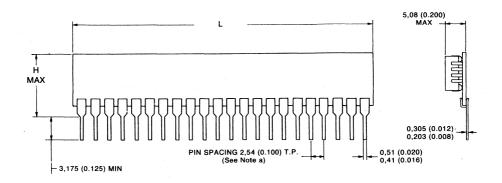

|     | MECHANIC     | AL DATA            |                | , . ,                                 | 11-          |

| WORDS         |                                                | BITS PER WORD                               |                                                                   |

|---------------|------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------|

| TURUS         | 1                                              | 4                                           | 8                                                                 |

| 1K            |                                                | (4K)<br><u>SRAMs</u><br>TMS2114<br>TMS2114L | (8K) <u>EPROMs</u> TMS2708 TMS27L08 SMJ2708 SMJ27L08              |

| 2K            |                                                |                                             | (16K) SRAMs EPROMs TMS4016 TMS2516 SMJ5517 SMJ2516 TMS2716        |

| 4K            | (4K)<br><u>SRAMs</u><br>TMS4044<br>TMS40L44    |                                             | (32K) ROMs EPROMs TMS4732 TMS2532 SMJ2532 TMS2732A                |

| 8K            |                                                |                                             | (64K) ROMs EPROMs TMS4664 TMS2564 TMS4764 SMJ2564 TMS4964 TMS2764 |

| 16K           | (16K)<br><u>DRAMs</u><br>TMS4116               | (64K)<br><u>DRAMs</u><br>TMS4416<br>SMJ4416 | (128K) ROMs EPROMs TMS47128 TMS27128                              |

| 32K           |                                                |                                             | (256K)<br><u>ROMs</u><br>TMS47256                                 |

| 64K           | DRAMs<br>TMS4161<br>TMS4164<br>SMJ4164         | (256K)<br><u>DRAMs</u><br>TMS4464           |                                                                   |

| 25 <b>6</b> K | (256K)<br><u>DRAMs</u><br>TM\$4256<br>TM\$4257 |                                             |                                                                   |

(Numbers in parenthesis indicate overall complexity.)

| Alphanumeric Index, Table of Contents, Selection Guide | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interchangeability Guide                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Glossary/Timing Conventions/Data Sheet Structure       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                        | 14 to 15 to |

| Dynamic RAM and Memory Support Devices                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Dynamic RAM Modules                                    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EPROM Devices                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ROM Devices                                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Static RAM and Memory Support Devices                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Applications Information                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Logic Symbols                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

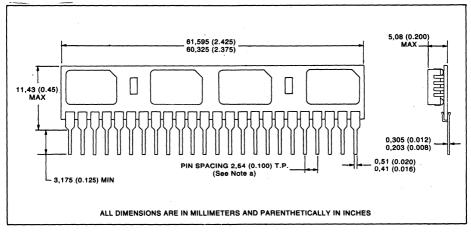

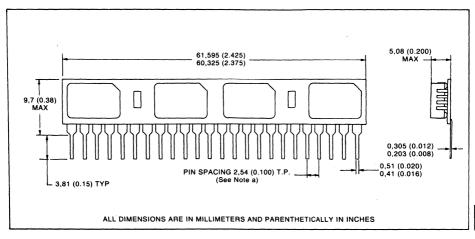

| Mechanical Data                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

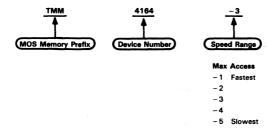

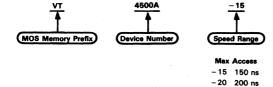

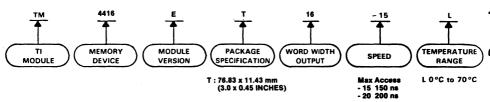

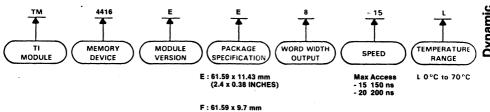

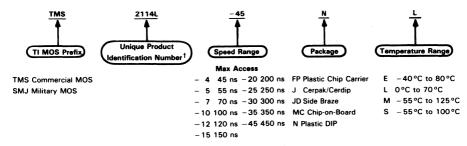

# PART 1 - ALTERNATE VENDOR PART NUMBERING (EXAMPLES)

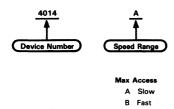

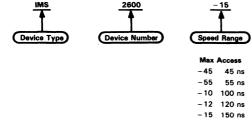

## **TEXAS INSTRUMENTS (TI)**

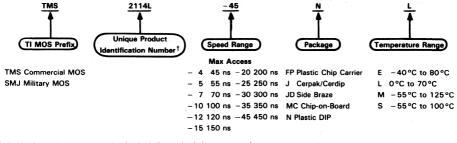

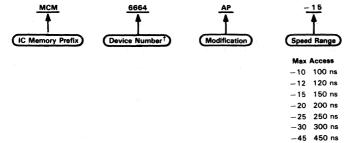

## EXAMPLE:

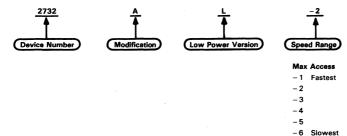

<sup>†</sup> Inclusion of an "L" in the product identification indicates the device operates at low power.

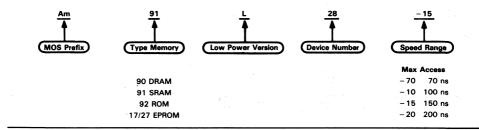

# **ADVANCED MICRO DEVICES (AMD)**

# **AMERICAN MICROSYSTEMS, INC. (AMI)**

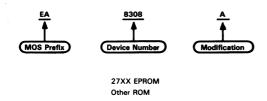

# **ELECTRONIC ARRAYS, INC. (EA)**

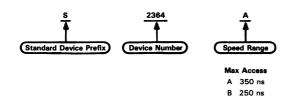

# EMM/SEMI

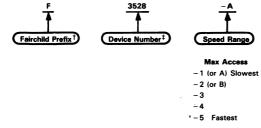

# **FAIRCHILD**

<sup>&</sup>lt;sup>†</sup> May be omitted.

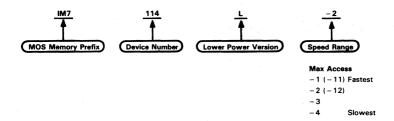

<sup>&</sup>lt;sup>‡</sup> Inclusion of an "L" indicates low power version.

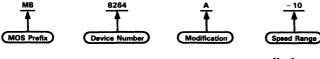

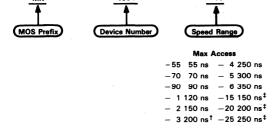

# **FUJITSU**

MB Fujitsu

MBM Industry Standard Prefix

-10 100 ns -12 120 ns -15 150 ns

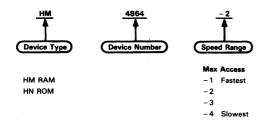

## **HITACHI**

# **INMOS**

INTEL

# INTERSIL/AMS

# **MOSTEK**

<sup>† 550</sup> ns for SRAMs and ROMs

<sup>‡</sup> DRAMs

# **MOTOROLA**

<sup>†</sup> Inclusion of an "L" indicates low power version.

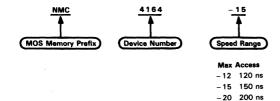

## **NATIONAL SEMICONDUCTOR**

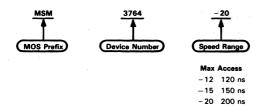

# OKI SEMICONDUCTOR (OKI)

# NIPPON ELECTRIC CORPORATION (NEC)

Max Access

- -0 200 ns

- -1 250 ns

- -2 100 ns

- -3 150 ns

# **SIGNETICS**

- -20 200 ns

- -25 250 ns

- -30 300 ns

- -45 450 ns

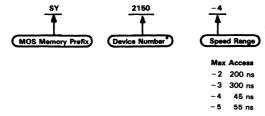

# **SYNERTEK**

<sup>\*</sup>Inclusion of an alpha character indicates a device modification.

# **TOSHIBA**

# **VLSI TECHNOLOGY**

-25 250 ns

## PART II - SECOND SOURCES\*

\*Based on available published data. (Official second sourcing agreements not necessarily implied.) All devices listed operate over the 0°C to 70°C temperature range.

# DYNAMIC RAMS

VENDOR PART NUMBER ORGANIZATION **MAX ACCESS** SECOND SOURCES TI TMS4116 16K×1 Max Access = 250 ns TI (3 Supply) AMD Am9016 Fairchild F4116 Fujitsu MB8116 Hitachi HM4716A Intersil IM4116 ITT ITT4116 Mitsubishi M5K4116 MK4116 Mostek Motorola MCM4116B National MM5290 NEC μPD416 TMM416 Toshiba 64K × 1 Max Access = 200 ns TMS4164<sup>†</sup> F4164 (5 V) Fairchild Fujitsu MB8264A Hitachi HM4864 INMOS IMS2600<sup>†</sup> 2164 Intel Micron Tech. MT4264<sup>†</sup> Mitsubishi M5K4164 MK4564 Mostek MCM6665 Motorola National NMC4164<sup>†</sup> NEC μPD4164 OKI MSM3764 Toshiba TMM4164 16K × 4 Max Access = 200 ns TMS4416 MB81416 (5 V) Fujitsu Hitachi HM48416AP INMOS IMS2620 256K×1 Max Access = 200 ns TI TMS4256/TMS4257 (5 V) Fujitsu MB81257/MB81256 HM50257 Hitachi Mitsubishi MSM4256 Motorola MCM6256 NEC μPD41256/μPD41257 OKI MSM37256 Toshiba TMM41256 Western Electric WCM41256

<sup>&</sup>lt;sup>†</sup>These devices have a 256 cycle, 4 ms refresh scheme. All others refresh in 2 ms.

# STATIC RAMS

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VENDOR |                |                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|------------------|

| ORGANIZATION | MAX ACCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TI     | SECOND SOURCES | PART NUMBER      |

| 4K×1         | Max Access = 450 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TI     |                | TMS4044/TMS40L44 |

| (5 V)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | AMD            | Am4044           |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | Intersil       | IM7141/IM7141L   |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | Intel          | 2141/2141L       |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | National SC    | MM2141           |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | Mitsubishi     | M5T4044          |